Schematic Design in Xilinx ISEĬlone the project and checkout commit 5c385071530140074c8aa53dc40297b752ab0bd7: Hence the circuit performs rotation operation for register B_REG. The least significant bit of B_REG is fed to the input of the most significant bit of B_REG. For this purpose one D-type flip-flop is used as a temporary storage element.

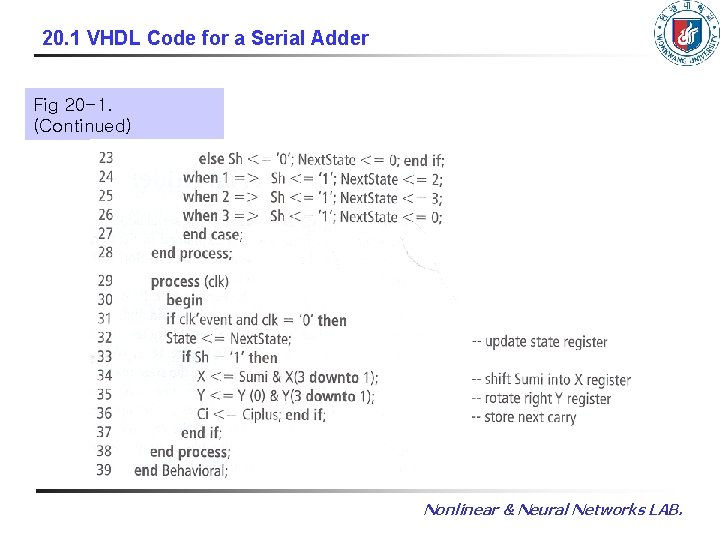

#SERIAL ADDER VHDL CODE FULL#

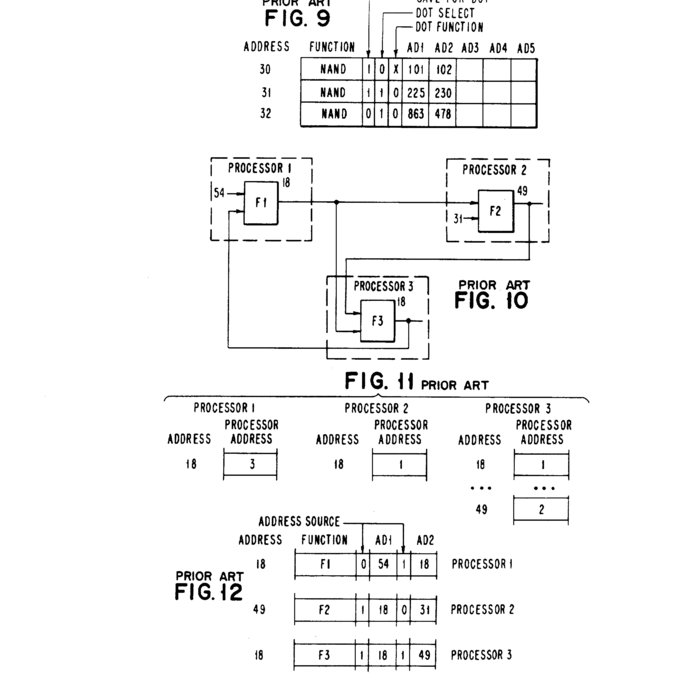

Carry-out output produced after each cycle is fed back to the full adder as a carry-in of the next significant bit. The sum is stored at the most significant bit of register A_REG. Starting with the least significant bit, at each cycle one bit of number A and one bit of number B are being added. The addition of numbers stored in A_REG and B_REG requires 4 cycles. After loading registers with numbers, shifting mode should be enabled to perform the arithmetic operation. Loading of numbers from inputs A, B to registers A_REG, B_REG occurs in one clock cycle. In order to load registers A_REG and B_REG with numbers, shift capability of the registers should be disabled and loading mode should be enabled. Two right-shift registers with parallel load, “A” and “B” a full adder FA, and a D-type flip-flop for storing carry-out are used.

#SERIAL ADDER VHDL CODE SERIAL#

A simplified schematics of the circuit is shown below: Simplified schematics of the 4-bit serial adder with parallel load. The CircuitĪ 4-bit serial adder circuit consists of two 4-bit shift registers with parallel load, a full adder, and a D-type flip-flop for storing carry-out. All code is written for Basys2 development board and Xilinx ISE was used as a synthesizer/simulator. However, basic understanding of the circuits is necessary, so both schematics and VHDL implementations are given.

"4-bit Serial Adder/Subtractor with Parallel Load" is a simple project which may help to understand use of variables in the "process" statement in VHDL. This is a tutorial I wrote for the "Digital Systems Design" course as an introduction to sequential design.

0 kommentar(er)

0 kommentar(er)